Parasitic inductances of the ground connection and of the guard ring... | Download Scientific Diagram

Guard rings: Structures, design methodology, integration, experimental results, and analysis for RF CMOS and RF mixed signal BiCMOS silicon germanium technology - ScienceDirect

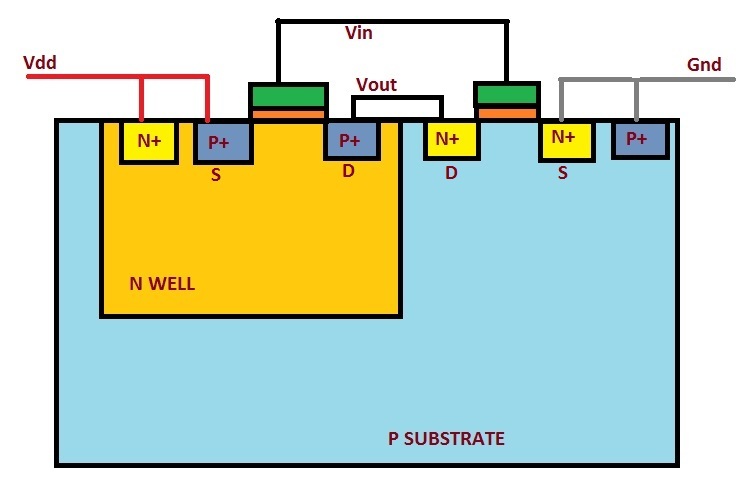

18. (a) Layout example of an inverter output buffer in the I/O cell... | Download Scientific Diagram

Guard rings: Structures, design methodology, integration, experimental results, and analysis for RF CMOS and RF mixed signal BiCMOS silicon germanium technology - ScienceDirect

Guard rings: Structures, design methodology, integration, experimental results, and analysis for RF CMOS and RF mixed signal BiCMOS silicon germanium technology - ScienceDirect

Guard rings: Structures, design methodology, integration, experimental results, and analysis for RF CMOS and RF mixed signal BiCMOS silicon germanium technology - ScienceDirect

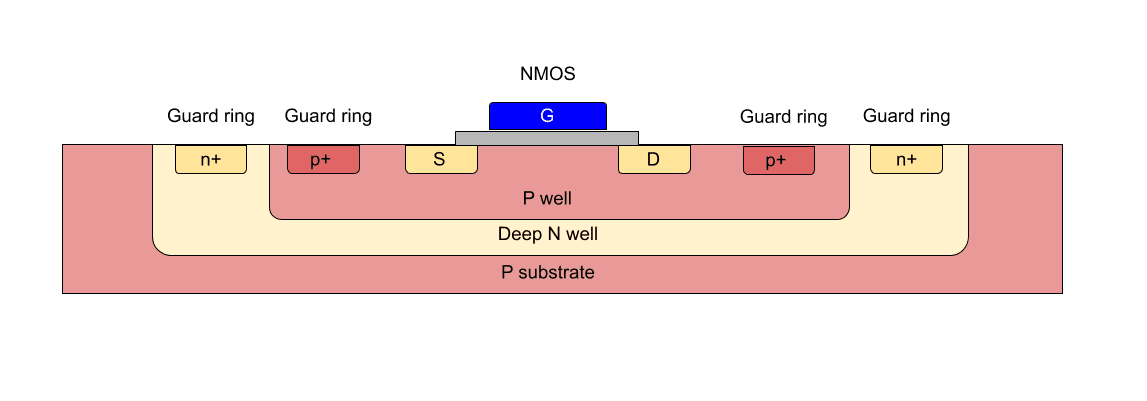

Figure 1 from Guard Ring Interactions and their Effect on CMOS Latchup Resilience | Semantic Scholar

Figure 3 from P-minus substrate guard ring modeling for the purpose of noise isolation in CMOS substrates | Semantic Scholar

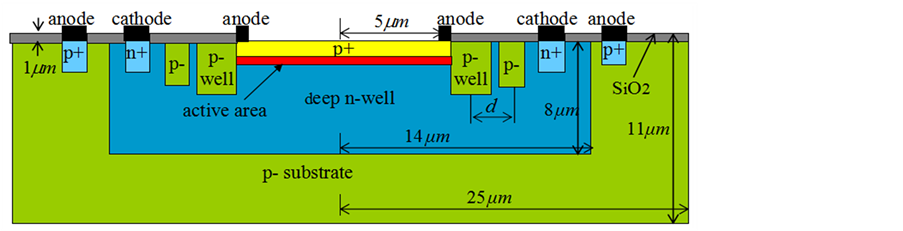

![The cross-section of a SPAD CMOS sensor [51] showing the guard ring... | Download Scientific Diagram The cross-section of a SPAD CMOS sensor [51] showing the guard ring... | Download Scientific Diagram](https://www.researchgate.net/profile/Maurice-Cheung-2/publication/221914021/figure/fig2/AS:305089412648961@1449750392057/The-cross-section-of-a-SPAD-CMOS-sensor-51-showing-the-guard-ring-surrounding-the.png)

The cross-section of a SPAD CMOS sensor [51] showing the guard ring... | Download Scientific Diagram